Bubble Sort (CPR E 281)

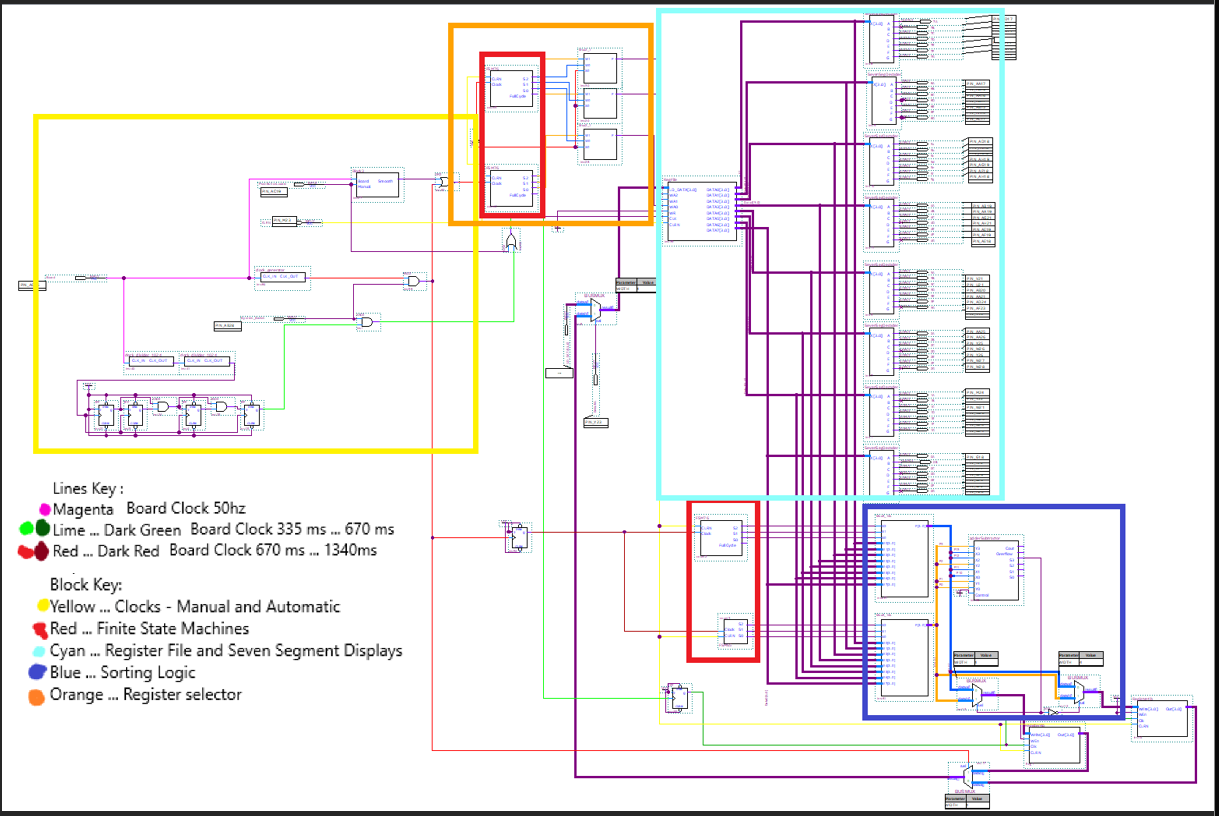

Digital logic final project: register file + FSM-based bubble sort design.

Project overview

Overview

- Built a register-file based design to load and display eight values.

- Designed dual FSM approach to select adjacent registers for bubble sort comparisons.

- Implemented compare/swap logic with adder/subtractor and auxiliary registers.

How It Worked

- Register file held eight 3-bit numbers; FSM logic selected registers for compare/swap operations.

- Comparator implemented via adder/subtractor (2's complement) to determine ordering based on sign bit.

- Auxiliary registers buffered values during swap/writeback.

Challenges

The main blocker was timing: difficulty writing to two registers within one clock cycle, requiring multiple clock domains and careful sequencing.

Add top-level block diagram and FSM state diagrams.

Add top-level block diagram and FSM state diagrams.

Design Documents

Files:

If you want to attach reports, PDFs, or datasheets, drop them into

/assets/docs/ and link them here.